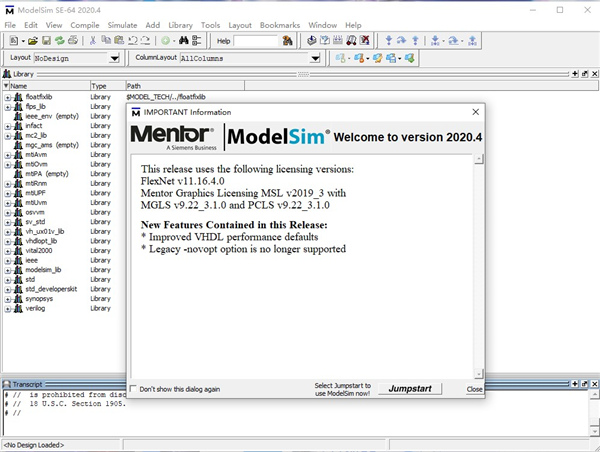

ModelSim SE 2020是一個專業的HDL語言仿真軟件,是業界唯一的單內核支持VHDL和Verilog混合仿真的仿真器。持PC、UNIX和LINUX混合平臺,可以很好的幫助用戶在多個不同的平臺進行仿真編譯。有著高級代碼覆蓋率,為系統驗證提供了有價值的指標,可以使用分析代碼覆蓋率數據的覆蓋實用程序,例如合并和測試排名。覆蓋結果可以交互式查看,模擬后或多次模擬運行合并后查看。本次帶來的是破解版,可以激活為完整版。

軟件特色

1、統一的混合語言仿真引擎,易于使用和性能。

2、native支持的Verilog,SystemVerilog的設計,VHDL和SystemC對復雜的設計環境的有效核查。

3、快速調試時間,易于使用的多語言調試環境。

4、先進的代碼覆蓋率和分析工具,可快速縮短覆蓋范圍。

5、提供了交互式調試和后期模擬調試,因此可使用相同的調試環境。

6、強大的波形比較功能,可輕松分析差異和錯誤。

7、統一的覆蓋數據庫,具有完整的交互式和HTML報告和處理功能,可了解和調試整個項目的覆蓋范圍。

8、結合HDL Designer和HDL Author進行完整的設計創建,項目管理和可視化功能。

安裝方法

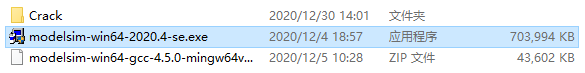

1、下載軟件壓縮包后先進行解壓,得到以下文件,雙擊運行“modelsim-win64-2020.4-se.exe”文件安裝軟件,如下圖;

2、等待軟件加載,進入軟件安裝向導頁,點擊下一步安裝軟件,如下圖;

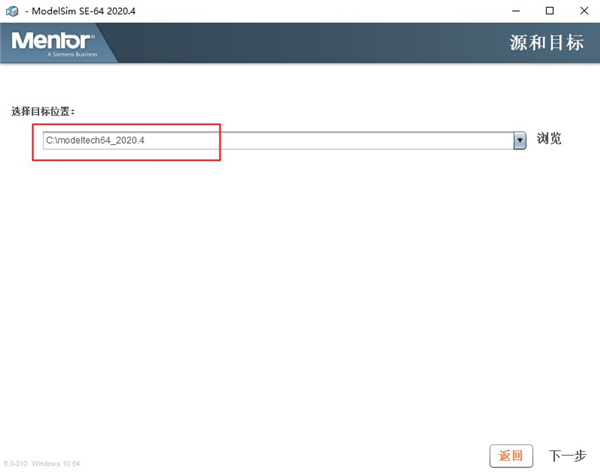

3、選擇軟件安裝的路徑,默認C盤,可更改,確認之后,點擊下一步即可;

注意默認安裝路徑的話會彈出創建路徑提示框,想要安裝在C盤的朋友點擊“是”即可;

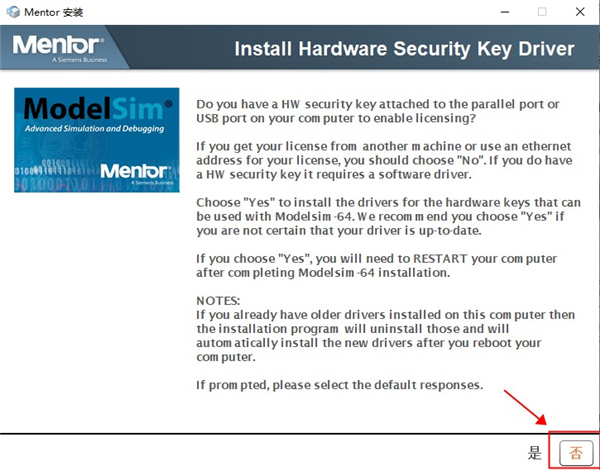

4、進入下一步之后,彈出下圖情況情況,注意,這里不要安裝Key Driver,點擊否;

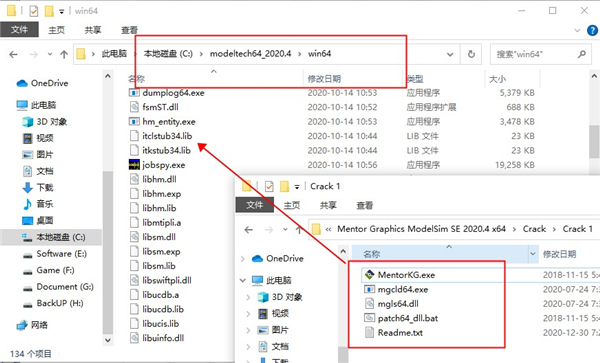

5、等到軟件安裝,軟件安裝完成后先不要運行軟件,然后打開crack文件夾,找到crack1文件夾,將里面的“MentorKG.exe、MGLS.DLL和patch_dll.bat”文件復制到軟件安裝路徑選擇的win64文件夾中;

默認安裝路徑為【C:\modeltech64_2020.4】

注:如果不知道前面安裝的路徑,可以右擊一下桌面的軟件快捷圖標,找到“打開軟件安裝位置"就可以打開軟件安裝的目標路徑。

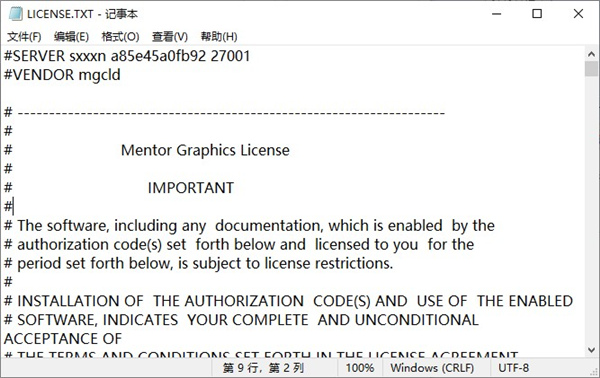

6、然后在替換軟件安裝的路徑下,以管理員的身份運行“patch_dll.bat”文件,然后將生成的許可證另存為“LICENSE.TXT”,并將其保存中軟件安裝的路徑下;

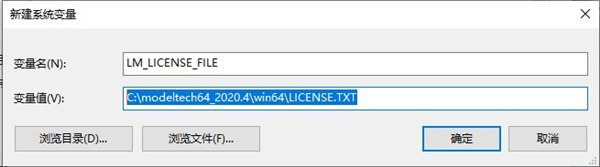

7、然后就是創建系統環境的變量;

變量名:LM_LICENSE_FILE

變量值:LICENSE.TXT的路徑。

默認為:C:\modeltech64_2020.4\win64\LICENSE.TXT

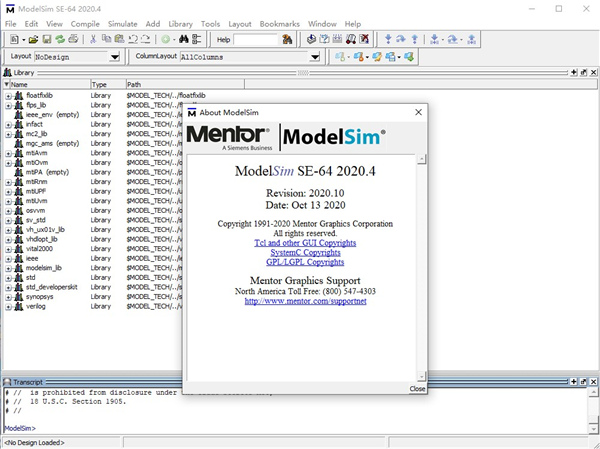

8、完成以上操作后,軟件就破解激活成功了;

軟件功能

1、更智能的GUI

智能設計的GUI可以有效利用桌面空間。 ModelSim提供了高度直觀的交互式圖形元素(窗口,工具欄,菜單等)排列方式,使您可以輕松查看和訪問其許多強大功能。 結果便是易于使用且可以快速掌握的功能豐富的GUI。 通過將Tcl用戶界面集成到其HDL仿真器中,ModelSim重新定義了仿真的開放性。 Tcl是一種簡單但功能強大的腳本語言,用于控制和擴展應用程序。

ModelSim GUI提供高效的設計調試和分析功能以及項目和文件管理。

2、記憶窗

存儲器窗口允許直觀,靈活地查看和調試設計存儲器。 VHDL和Verilog內存是從源中自動提取并在GUI中查看的,從而提供了強大的搜索,填充,編輯,加載和保存功能。內存窗口支持從文件或通過使用恒定,隨機和計算值來預加載內存,從而節省了僅加載內存來初始化測試平臺部分的耗時步驟。所有功能都可以通過命令行使用,從而可以在腳本中使用它們。

3、波形和結果查看

ModelSim提供了高性能的全功能波形窗口。 Wave窗口提供了用于標記有趣的時間點并測量光標之間的時間距離的光標。波形窗口的內容可以通過強大的虛擬信號定義和分組靈活地設置格式。

在兩個仿真結果之間可以輕松進行波形比較。通過用戶指定的時間過濾功能,可以輕松處理RTL和門級仿真結果之間的時序差異。

ModelSim提供了獨特的WLF管理實用程序(又名WLFMAN),該實用程序允許處理WLF結果文件。這使您可以指定要記錄到WLF文件的信息量,并允許您根據信號或時間對現有WLF文件進行子集化。

WLFMAN實用程序可有效管理磁盤空間并提高模擬后調試效率。

4、源窗口模板和向導

使用VHDL和Verilog模板和向導,您可以快速開發HDL代碼,而不必記住確切的語言語法。只需單擊鼠標,即可使用所有語言結構。易于使用的向導將引導您逐步完成更復雜的HDL塊的創建。向導顯示了如何創建可參數化的邏輯塊,測試臺激勵和設計對象。源代碼窗口模板和向導通過省時的快捷方式使新手和高級HDL開發人員受益。

5、專案經理

項目管理器大大減少了組織文件和庫所需的時間。在編譯和模擬時,項目管理器會存儲每個項目的唯一設置,使您可以從上次中斷的地方重新啟動模擬器。仿真屬性使您可以輕松地使用預先配置的參數進行仿真。

6、代碼覆蓋率

設計驗證的完整性可以通過代碼覆蓋率來衡量。 ModelSim支持語句,表達式,條件,切換和FSM覆蓋范圍。代碼覆蓋率指標是從HDL源自動得出的。由于創建了許多可配置和可重復使用的設計模塊,并且并非所有指標都很有價值,因此可以使用代碼覆蓋率瀏覽器中指定的源代碼實用程序和排除項來靈活管理代碼覆蓋率指標。

7、基于斷言的驗證

ModelSim提供了一個全面的,基于標準的基于斷言的驗證(ABV)解決方案,可以選擇SystemVerilog斷言(SVA),屬性規范語言(PSL)或兩者。

8、強大的,具有成本效益的模擬

解決方案ModelSim提供了功能強大的仿真解決方案,非常適合驗證中小型FPGA設計;尤其是具有復雜任務關鍵功能的設計。

更新日志

1、在2020.4中修復了SystemVerilog缺陷;

2、QSIM-64922-Vlog報告了錯誤;

3、65962-如果在編譯時使用-autoorder和-quiet開關,如果語義錯誤在刷新階段遇到錯誤,將不會打印錯誤。

4、QSIM-66278-如果占用超過2G的空間的大型數據結構將崩潰使用默認初始化。

5、QSIM-65639-design.bin的信號范圍可能不正確。

相關版本

?電路的設計在生產中是很關鍵的,電路設計仿真軟件在電子工程和電子學教育中扮演著至關重要的角色,它們幫助工程師和學生通過模擬電路的實際工作狀態來驗證設計的正確性。

精品推薦

-

Altium Designer10破解工具

詳情 -

MasterCAM X9注冊機

詳情 -

Altium Designer綠色版

詳情 -

MasterCAM9.1漢化版

詳情 -

Master Cam 2020

詳情 -

Master Cam 2017完整漢化包

詳情 -

Multisim14元件庫大全

詳情 -

Proteus仿真軟件

詳情 -

奎享雕刻

詳情 -

機械工程師CAD2020企業版破解

詳情 -

邁迪三維設計工具集6.0注冊碼破解版

詳情 -

FastCAM套料軟件

詳情 -

WECON LEVI Studio

詳情 -

Protel99SE全中文版支持win10

詳情 -

Master Cam 2017

詳情 -

浩辰CAD機械2022永久激活版

詳情

裝機必備軟件

網友評論