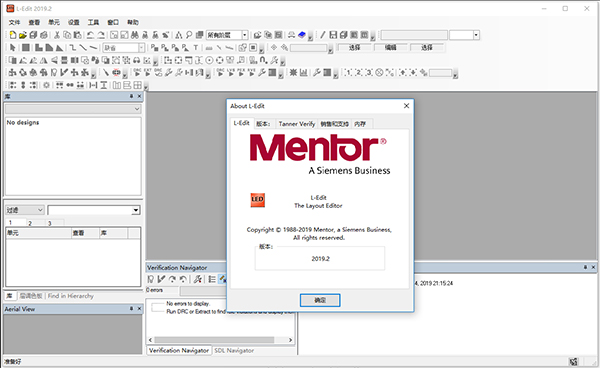

Tanner Tools 2019功能強(qiáng)大的電路設(shè)計(jì)軟件,適用于集成電路(IC)、模擬/混合信號(hào)(AMS)和MEMS設(shè)計(jì)。2019版本進(jìn)行了全面升級(jí)和優(yōu)化,提供了緊密集成的混合信號(hào)設(shè)計(jì)套件,設(shè)計(jì)周期極短、性價(jià)比高,特別適合物聯(lián)網(wǎng)和基于項(xiàng)目的設(shè)計(jì),以一種高度集成的端到端流程支持進(jìn)行快速的電路設(shè)計(jì)、模擬和混合信號(hào)IC、MEMS和光子設(shè)計(jì)等。這里帶來(lái)的是破解版,下面有著詳細(xì)的破解教程。

軟件特色

1、繼承的連接

S-Edit現(xiàn)在提供對(duì)通過(guò)參數(shù)化電源/接地符號(hào)或網(wǎng)絡(luò)標(biāo)簽定義的繼承連接的支持。

2、符號(hào)和示意圖中的圖像

現(xiàn)在可以在符號(hào)視圖和示意圖視圖中插入圖像。這可以用于創(chuàng)建更詳細(xì)的符號(hào),也可以用于在示意圖中添加注釋或文檔。 Windows®支持位圖和矢量格式。 Linux僅支持位圖格式。

3、AFS和EZWave集成

S-Edit現(xiàn)在與AFS,Eldo和EZwave集成在一起,以在整個(gè)Linux環(huán)境中提供仿真設(shè)置,啟動(dòng),交叉探測(cè)和向后注釋支持。 Windows上的SEdit和Linux上使用PSF輸出格式的AFS / EZWave現(xiàn)在也支持設(shè)置和啟動(dòng),交叉探測(cè)和向后注釋。反向注釋支持包括DC OP V / I,AC小信號(hào),模型參數(shù),設(shè)備AC小信號(hào)參數(shù)表和設(shè)備參數(shù)反向注釋。

4、布局偽造

Layout Forge是一種生產(chǎn)力增強(qiáng)工具,適用于模擬布局設(shè)計(jì)人員執(zhí)行設(shè)備級(jí)別的布局和布線,從而可以完全控制布局和布線。 Layout Forge在原理圖中識(shí)別差分對(duì),電流鏡和共源共柵電流鏡,并自動(dòng)在布局中生成放置和布線的單元。設(shè)計(jì)人員可以在瞬間中心的幫助下自定義設(shè)備的放置,并可以自定義工藝路線。

5、鄰接

參數(shù)化的單元鄰接可以允許參數(shù)化的單元實(shí)例在鄰接時(shí)調(diào)整其幾何形狀以占據(jù)最小面積。例如,如果一個(gè)n溝道MOSFET的兩個(gè)實(shí)例共享相同的源極或漏極,則基臺(tái)將重新生成實(shí)例,以去除額外的觸點(diǎn)并使這兩個(gè)器件彼此非常靠近。基臺(tái)將檢查有效的連接,相同類型或類別的設(shè)備,并確保LVS清潔結(jié)果。必須由PDK中的鑄造廠啟用參數(shù)化的單元橋臺(tái)。

安裝方法

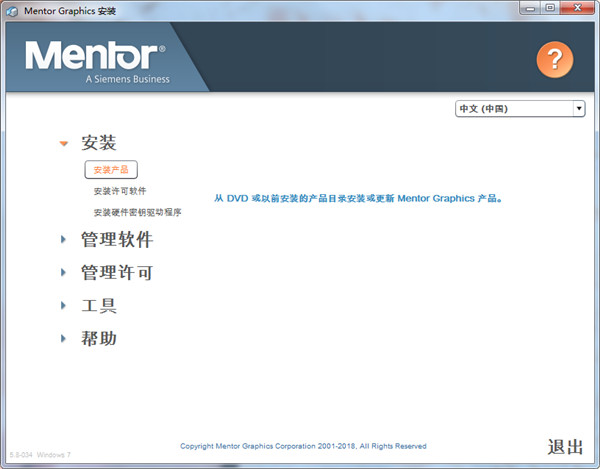

1、下載安裝包,解壓縮并運(yùn)行安裝,選擇安裝產(chǎn)品

2、選擇軟件安裝位置

3、選擇需要安裝的產(chǎn)品,自行勾選即可

4、閱讀軟件許可協(xié)議,點(diǎn)擊同意

5、一切準(zhǔn)備就緒,點(diǎn)擊安裝

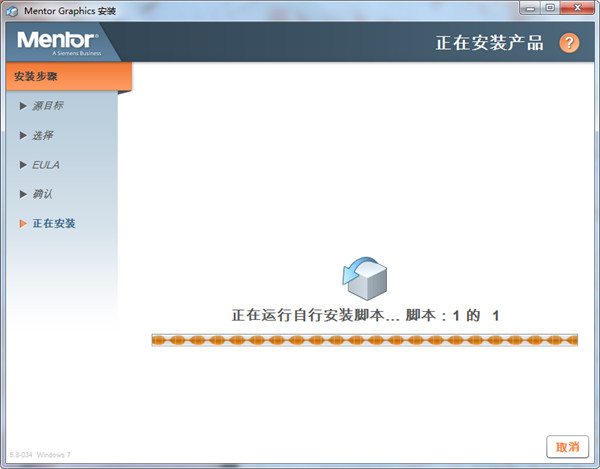

6、正在安裝中,請(qǐng)耐心等待一會(huì)

7、安裝成功,退出安裝向?qū)?/p>

8、右鍵管理員身份運(yùn)行MentorKG.exe,會(huì)自動(dòng)生成LICENSE.TXT,保存在一個(gè)指定位置,比如安裝目錄下

9、右鍵我的電腦——>屬性——>高級(jí)系統(tǒng)設(shè)置——>環(huán)境變量,創(chuàng)建系統(tǒng)環(huán)境變量

變量名:LM_LICENSE_FILE

變量值:指向LICENSE.TXT路徑

10、運(yùn)行軟件即可免費(fèi)使用了

軟件功能

1、完整的IC設(shè)計(jì)捕捉環(huán)境

Tanner S-Edit是一個(gè)易于使用的設(shè)計(jì)環(huán)境,用于原理圖捕獲和設(shè)計(jì)輸入。 它為您提供了處理最復(fù)雜的混合信號(hào)IC設(shè)計(jì)捕獲所需的功能。 S-Edit與Tanner T-Spice,Analog FastSPICE™(AFS)或Eldo®仿真器,Tanner L-Edit IC布局工具以及Calibre®LVS和PEX工具緊密集成。 S-Edit通過(guò)優(yōu)化您的生產(chǎn)率并加快將概念應(yīng)用于硅的速度,可以幫助您滿足當(dāng)今快速發(fā)展的市場(chǎng)的需求。 更快的設(shè)計(jì)周期為您提供了向最佳解決方案過(guò)渡的更多靈活性,從而節(jié)省了更多時(shí)間和資源來(lái)進(jìn)行工藝角確認(rèn)。 結(jié)果是減少了下游風(fēng)險(xiǎn),提高了產(chǎn)量并縮短了上市時(shí)間。

2、最復(fù)雜的混合信號(hào)IC設(shè)計(jì)的原理圖捕獲

總線支持加快了混合信號(hào)設(shè)計(jì)的創(chuàng)建

先進(jìn)的陣列支持可輕松創(chuàng)建和編輯具有重復(fù)塊的存儲(chǔ)器,圖像或電路

具有快速固定(熱點(diǎn))功能的橡皮筋連通性編輯功能可加快設(shè)計(jì)修改速度

S-Edit在設(shè)計(jì)過(guò)程中實(shí)時(shí)顯示評(píng)估的參數(shù); 可以顯示或評(píng)估具有基于其他電路參數(shù)的公式的參數(shù)

自動(dòng)生成符號(hào)使您可以輕松地從原理圖創(chuàng)建符號(hào)并同步所有更改

所有操作均可通過(guò)TCL / Tk命令語(yǔ)言完全編寫腳本

可記錄的腳本使您能夠自動(dòng)化任務(wù)或擴(kuò)展工具以滿足特定于應(yīng)用程序的需求

可重播的日志可在網(wǎng)絡(luò)或硬件出現(xiàn)意外故障時(shí)進(jìn)行恢復(fù)

S-Edit在突出顯示層次結(jié)構(gòu)時(shí)執(zhí)行網(wǎng)絡(luò)突出顯示并保持網(wǎng)絡(luò)突出顯示

口徑RVE在原理圖,布局和LVS報(bào)告之間進(jìn)行交叉探測(cè)以突出顯示網(wǎng)絡(luò)或設(shè)備

原理圖ERC使您可以檢查設(shè)計(jì)中是否存在常見(jiàn)錯(cuò)誤,例如未驅(qū)動(dòng)的網(wǎng)絡(luò),未連接的引腳以及由多個(gè)輸出驅(qū)動(dòng)的網(wǎng)絡(luò)。 設(shè)計(jì)檢查是完全可配置的,包括自定義驗(yàn)證腳本

3、與仿真緊密集成

從原理圖捕獲環(huán)境中驅(qū)動(dòng)模擬器。 這樣就可以直接在原理圖上查看工作點(diǎn)結(jié)果,查看設(shè)備的小信號(hào)參數(shù),查看模型參數(shù)以及執(zhí)行波形交叉探測(cè)以查看節(jié)點(diǎn)電壓以及設(shè)備端子電流或電荷。

S-Edit為電路設(shè)計(jì),仿真,分析和調(diào)整的迭代循環(huán)創(chuàng)建了高效流程。 專注于設(shè)計(jì)而不是數(shù)據(jù)處理,從而加快了設(shè)計(jì)過(guò)程。

4、與第三方工具和舊版數(shù)據(jù)輕松互操作

S-Edit從第三方工具中以本機(jī)OpenAccess或EDIF進(jìn)行讀取,并自動(dòng)轉(zhuǎn)換原理圖和屬性以無(wú)縫集成遺留數(shù)據(jù)

網(wǎng)表可以以靈活的,用戶可配置的格式導(dǎo)出,包括SPICE和CDL變體,EDIF,結(jié)構(gòu)性Verilog 以及結(jié)構(gòu)化的VHDL

S-Edit中的庫(kù)支持最大限度地重用了以前項(xiàng)目中開發(fā)的或從第三方供應(yīng)商處導(dǎo)入的IP

5、強(qiáng)大且易于使用的界面

S-Edit使前端設(shè)計(jì)的捕獲更輕松,更高效

完全由用戶可編程的設(shè)計(jì)環(huán)境使您可以重新映射熱鍵,創(chuàng)建新的工具欄以及根據(jù)自己的喜好自定義視圖-所有這些都在簡(jiǎn)化的GUI中

完整的用戶界面 支持多種語(yǔ)言,包括英語(yǔ),日語(yǔ),簡(jiǎn)體中文和繁體中文

S-Edit提供Unicode支持; 所有用戶數(shù)據(jù)都可以輸入國(guó)際字符集。ird-PartyTools and Legacy Data

S-Edit從第三方工具中以本機(jī)OpenAccess或EDIF進(jìn)行讀取,并自動(dòng)轉(zhuǎn)換原理圖和屬性以無(wú)縫集成遺留數(shù)據(jù)

網(wǎng)表可以以靈活的,用戶可配置的格式導(dǎo)出,包括SPICE和CDL變體,EDIF,結(jié)構(gòu)性Verilog 以及結(jié)構(gòu)化的VHDL

S-Edit中的庫(kù)支持最大限度地重用了以前項(xiàng)目中開發(fā)的或從第三方供應(yīng)商處導(dǎo)入的IP

6、具有成本效益

S-Edit提供了理想的性能成本比,使您可以最大化項(xiàng)目中的設(shè)計(jì)人員人數(shù)

由于S-Edit在Windows®和Linux平臺(tái)上運(yùn)行,因此設(shè)計(jì)人員可以在具有成本效益的工作站或 筆記本電腦 這意味著您可以隨身攜帶您的工作,甚至在家中,也可以繼續(xù)工作,以滿足上市時(shí)間的壓力

提供兩種配置:完整的原理圖編輯器和原理圖查看器

標(biāo)簽: 電路設(shè)計(jì)

?電路的設(shè)計(jì)在生產(chǎn)中是很關(guān)鍵的,電路設(shè)計(jì)仿真軟件在電子工程和電子學(xué)教育中扮演著至關(guān)重要的角色,它們幫助工程師和學(xué)生通過(guò)模擬電路的實(shí)際工作狀態(tài)來(lái)驗(yàn)證設(shè)計(jì)的正確性。

下載地址

精品推薦

-

Altium Designer10破解工具

詳情 -

MasterCAM X9注冊(cè)機(jī)

詳情 -

Altium Designer綠色版

詳情 -

MasterCAM9.1漢化版

詳情 -

Master Cam 2020

詳情 -

Master Cam 2017完整漢化包

詳情 -

Multisim14元件庫(kù)大全

詳情 -

Proteus仿真軟件

詳情 -

奎享雕刻

詳情 -

機(jī)械工程師CAD2020企業(yè)版破解

詳情 -

邁迪三維設(shè)計(jì)工具集6.0注冊(cè)碼破解版

詳情 -

FastCAM套料軟件

詳情 -

WECON LEVI Studio

詳情 -

Protel99SE全中文版支持win10

詳情 -

Master Cam 2017

詳情 -

浩辰CAD機(jī)械2022永久激活版

詳情

裝機(jī)必備軟件

網(wǎng)友評(píng)論