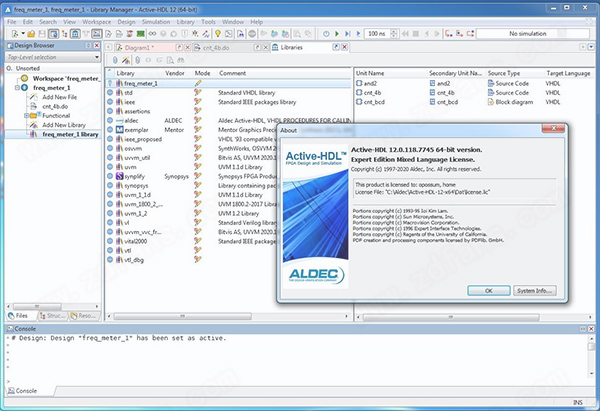

Aldec Active-HDL 12是一個(gè)專業(yè)的FPGA設(shè)計(jì)仿真平臺(tái),支持所有領(lǐng)先的C/HDL合成和實(shí)現(xiàn)工具,并且兼容業(yè)界標(biāo)準(zhǔn),如IEEE、ISO、IEC及其它標(biāo)準(zhǔn)等它都支持。可以給用戶帶來(lái)全面的設(shè)計(jì)覆蓋率。同時(shí)它還具備排錯(cuò)工具,能支援Soft或Hard IP Core元件。最新版本中增加了對(duì)開(kāi)源VHDL驗(yàn)證方法、還增強(qiáng)了SystemVerilog和對(duì)未解析的用戶定義的網(wǎng)絡(luò)類型的初步支持。更多強(qiáng)大的功能用戶可以自己下載體驗(yàn)。本次帶來(lái)的是中文破解版,下方有著詳細(xì)的安裝破解教程。

軟件功能

1、Aldec, Inc.是FPGA和ASIC設(shè)計(jì)的混合HDL語(yǔ)言仿真和硬件輔助驗(yàn)證的先驅(qū),已增強(qiáng)以支持VHDL-2019 (IEEE 1076-2019)中的新特性。這些特性簡(jiǎn)化了語(yǔ)言,解除了早期版本中存在的某些限制,并引入了新的應(yīng)用程序編程接口(api)。

2、還增強(qiáng)了SystemVerilog,包括對(duì)實(shí)例的多維數(shù)組的初步支持,對(duì)未解析的用戶定義的網(wǎng)絡(luò)類型的初步支持,以及對(duì)惟一約束的初步支持。

3、最新版本中也出現(xiàn)了一些對(duì)SystemVerilog的非標(biāo)準(zhǔn)擴(kuò)展。這包括允許由連續(xù)賦值驅(qū)動(dòng)可變類型的時(shí)鐘塊輸出,允許使用foreach循環(huán)遍歷子數(shù)組的元素,以及將帶modport的虛擬接口賦值給不帶modport的虛擬接口。

4、是為開(kāi)發(fā)VHDL、Verilog/SystemVerilog、EDIF和SystemC設(shè)計(jì)而設(shè)計(jì)的集成環(huán)境。它包含的幾個(gè)設(shè)計(jì)輸入工具,高密度脂蛋白/ SystemC編譯器單一仿真內(nèi)核,幾個(gè)標(biāo)準(zhǔn)和先進(jìn)的調(diào)試工具,圖形和文本仿真輸出的觀眾,和許多輔助工具設(shè)計(jì)設(shè)計(jì),便于管理、資源文件,和庫(kù)以及內(nèi)置的接口,允許運(yùn)行模擬、合成、或?qū)崿F(xiàn)本地或遠(yuǎn)程計(jì)算機(jī),控制源文件的修訂,或者與提供仿真模型的第三方工具通信。

5、提供了一組強(qiáng)大的向?qū)В梢苑奖愕貏?chuàng)建新的工作空間、設(shè)計(jì)或設(shè)計(jì)資源,包括VHDL、Verilog、SystemC源文件、塊或狀態(tài)圖、test長(zhǎng)凳等。

6、從圖形用戶界面執(zhí)行的大多數(shù)操作也可以通過(guò)軟件宏語(yǔ)言的命令調(diào)用。通過(guò)編寫自己的宏,可以顯著改進(jìn)測(cè)試和自動(dòng)化設(shè)計(jì)處理。軟件還為Perl和Tcl/Tk提供腳本引擎。通過(guò)創(chuàng)建用戶定義的腳本,您可以通過(guò)添加額外的窗口、擴(kuò)展宏語(yǔ)言以及提供外部工具和軟件產(chǎn)品的接口來(lái)增強(qiáng)Active-HDL 12設(shè)計(jì)環(huán)境。

7、套件還包括VSimSA,一個(gè)為批處理設(shè)計(jì)的獨(dú)立的VHDL/Verilog/SystemVerilog/EDIF/SystemC仿真環(huán)境。在功能上,VSimSA完全獨(dú)立于軟件。VSimSA與軟件的區(qū)別在于缺少圖形用戶界面(GUI)。VSimSA命令和程序完全由命令行發(fā)出和控制,這在自動(dòng)化設(shè)計(jì)測(cè)試中特別有用。

安裝方法

1.在本站下載好數(shù)據(jù)包后進(jìn)行解壓得到安裝程序“Active-HDL_12.0.118.7745_x64_main_setup.exe”,鼠標(biāo)雙擊運(yùn)行進(jìn)入安裝向?qū)c(diǎn)擊“next”進(jìn)入下一步

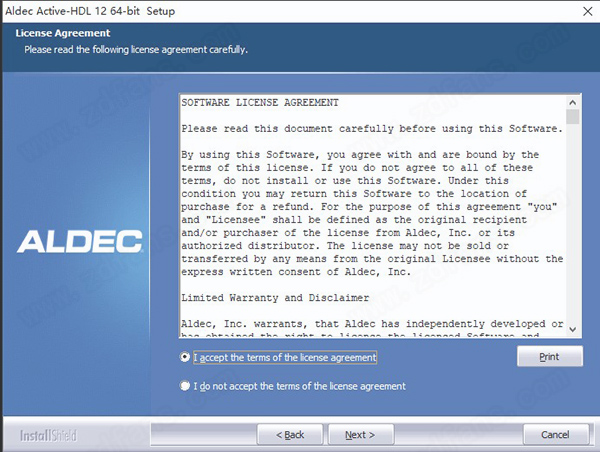

2.選擇第一項(xiàng)“I accept the terms of the license agreement”(我接受許可協(xié)議的條款),再點(diǎn)擊“next”進(jìn)入下一步

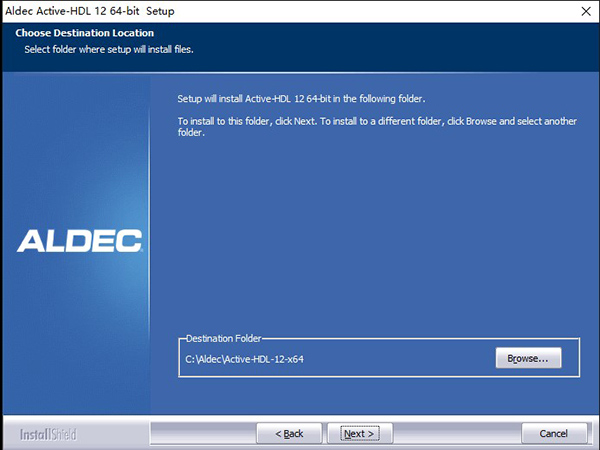

3.選擇安裝位置,默認(rèn)路徑為“C:\Aldec\Active-HDL-12-x64”,建議最好不要安裝到系統(tǒng)盤(C盤)

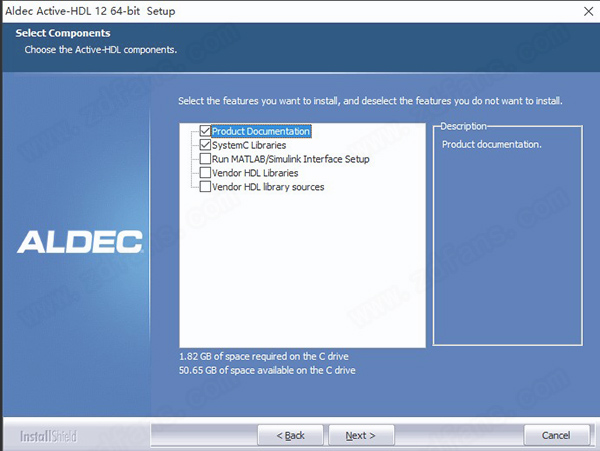

4.根據(jù)自身需求選擇安裝功能組件,需要安裝的前面勾上即可

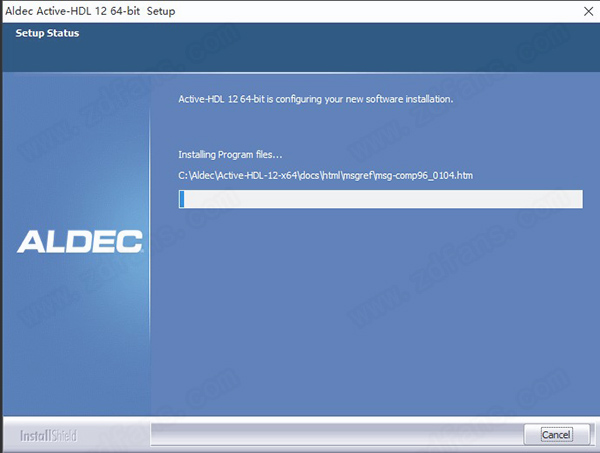

5.軟件安裝需要一些時(shí)間請(qǐng)耐心等待即可

6.當(dāng)安裝完成后點(diǎn)擊“finish”即可退出安裝向?qū)?/p>

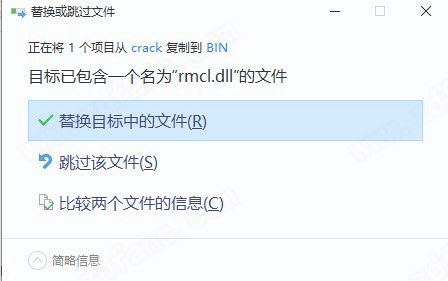

7.完成后先不要運(yùn)行軟件,回到剛才下載的數(shù)據(jù)包中將rmcl.dll復(fù)制到安裝目錄下的bin文件夾中,點(diǎn)擊替換目標(biāo)中的文件

8.記事本方式打開(kāi)license.dat,請(qǐng)確保將HOSTID = ANY_ID修改為您自己的名稱,例如HOSTID =3C-7C-3F-ED-62-66

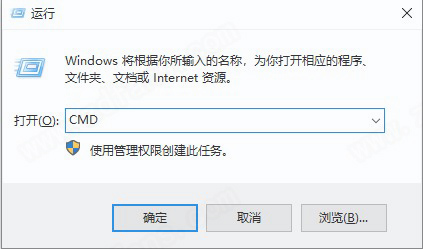

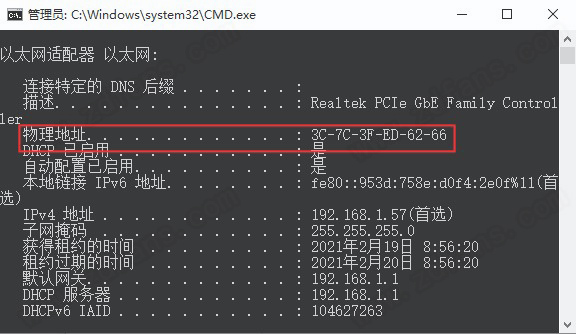

(1)我們首先需要知道電腦的HostID就是電腦的物理地址,按win+R鍵打開(kāi)運(yùn)行,輸入cmd,

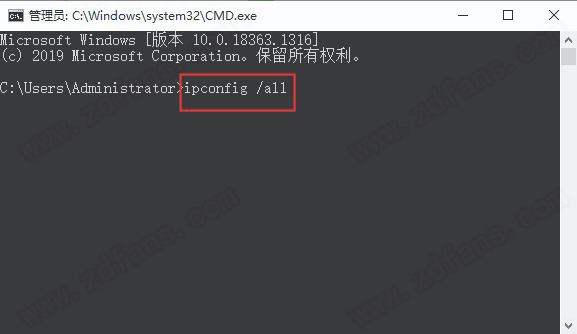

(2)第二步進(jìn)去命令提示符之后,輸入ipconfig /all,如下圖所示:

(3)第三步按回車鍵之后,可以看到電腦的物理地址也就是電腦的HostID,如下圖所示:

(4)小編的HostID為:3C-7C-3F-ED-62-66,這時(shí)以記事本的方式打開(kāi)“License.lic”,點(diǎn)擊“編輯”-“替換”,查找內(nèi)容輸入:原本的 HostID,替換內(nèi)容輸入“3C-7C-3F-ED-62-66”,最后點(diǎn)擊全部替換即可,保存退出!

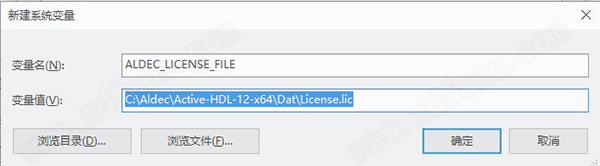

9.將“License.lic”復(fù)制到安裝目錄下DAT文件夾中

10.創(chuàng)建一個(gè)系統(tǒng)環(huán)境變量

變量名:ALDEC_LICENSE_FILE

變量值:license.dat的路徑(例如C:\Aldec\Active-HDL-11.1-x64\Dat\ license.dat)

11.最后運(yùn)行軟件即可直接免費(fèi)使用了

使用說(shuō)明

1、一般

在使用VITAL模型的設(shè)計(jì)初始化期間,僅在加載SDF文件時(shí)啟動(dòng)負(fù)約束計(jì)算階段。無(wú)論SDF文件的可用性如何,都應(yīng)啟動(dòng)此階段。

如果多次重新啟動(dòng)仿真,則可能會(huì)發(fā)生內(nèi)部存儲(chǔ)器碎片,導(dǎo)致內(nèi)存分配增加。(DKO2370)

如果在模擬運(yùn)行時(shí)關(guān)閉系統(tǒng)控制臺(tái)窗口而中斷VSimSA,則wave.asdb.error文件和wave.asdbw文件夾及其內(nèi)容將保留在磁盤上。這些是臨時(shí)項(xiàng)目,如果需要,用戶可以安全地刪除它們。此外,它們不會(huì)妨礙后續(xù)模擬會(huì)話,并在運(yùn)行新模擬時(shí)自動(dòng)刪除。

無(wú)論如何,建議通過(guò)發(fā)出endsim命令來(lái)結(jié)束模擬。(MRP3553)

2、Verilog模擬

只有將所有文件編譯到空設(shè)計(jì)庫(kù)中時(shí),頂級(jí)Verilog模塊的自動(dòng)檢測(cè)才能正常工作。頂級(jí)檢測(cè)不適用于單獨(dú)編譯的Verilog文件。

無(wú)法停止將信號(hào)記錄到波形文件中。一旦在模擬過(guò)程中將信號(hào)添加到波形文件中(使用trace或addwave命令),它將具有完整的歷史記錄,直到模擬結(jié)束。

具有隨機(jī)刺激器規(guī)范的$force任務(wù)不起作用(JKL59)。

3、SystemVerilog模擬

常規(guī)數(shù)組不能分配給動(dòng)態(tài)數(shù)組,反之亦然。

不支持使用文字的作業(yè)。

類C操作符(+=,++,-等)不能操作隊(duì)列/數(shù)組元素。

$sign不能用于引用隊(duì)列的最后一個(gè)元素。(它只能在聲明隊(duì)列時(shí)使用。)

foreach循環(huán)不能用于迭代數(shù)組/隊(duì)列元素。

系統(tǒng)功能,例如$size不適用于數(shù)組或隊(duì)列。

通過(guò)將點(diǎn)和字段名稱附加到索引名稱(即數(shù)組/隊(duì)列元素),無(wú)法訪問(wèn)類和結(jié)構(gòu)的字段。

數(shù)據(jù)容器不能放在結(jié)構(gòu)或類中。

動(dòng)態(tài)數(shù)組,關(guān)聯(lián)數(shù)組和隊(duì)列的常規(guī)數(shù)組不可用。

幾個(gè)對(duì)象類型(例如解壓縮的結(jié)構(gòu)或字符串)不能放在數(shù)組和隊(duì)列中。

數(shù)據(jù)容器不能通過(guò)引用傳遞

標(biāo)簽: 仿真設(shè)計(jì) FPGA設(shè)計(jì) 芯片開(kāi)發(fā)

下載地址

精品推薦

-

Altium Designer10破解工具

詳情 -

MasterCAM X9注冊(cè)機(jī)

詳情 -

Altium Designer綠色版

詳情 -

MasterCAM9.1漢化版

詳情 -

Master Cam 2020

詳情 -

Master Cam 2017完整漢化包

詳情 -

Multisim14元件庫(kù)大全

詳情 -

Proteus仿真軟件

詳情 -

奎享雕刻

詳情 -

SIMetrix SIMPLIS(電路仿真設(shè)計(jì)軟件)

詳情 -

邁迪三維設(shè)計(jì)工具集6.0注冊(cè)碼破解版

詳情 -

Master Cam 2017

詳情 -

WECON LEVI Studio

詳情 -

WinCC7.5硬狗破解文件

詳情 -

CGTech VERICUT 9

詳情 -

機(jī)械工程師CAD2020企業(yè)版破解

詳情

-

7 KiCad

裝機(jī)必備軟件

網(wǎng)友評(píng)論